Das Aufkommen von Chiplets • Artikel • Wissensschale, Chiplet -Design -Kits für die 3D -IC -heterogene Integration | Siemens -Software

Verwenden von Chiplet -Design -Kits, um den Weg für die heterogene 3D -IC -Integration zu ebnen

Contents

- 1 Verwenden von Chiplet -Design -Kits, um den Weg für die heterogene 3D -IC -Integration zu ebnen

- 1.1 Das Aufkommen von Chiplets

- 1.2 Präambel

- 1.3 Chiplet, Quésaco ?

- 1.4 Wirtschaftliche Aspekte von Chiplets

- 1.5 Zwei Beispiele: AMD und Intel (Altera)

- 1.6 Verwenden von Chiplet -Design -Kits, um den Weg für die heterogene 3D -IC -Integration zu ebnen

- 1.7 Aufbau eines Ökosystems für erfolgreiche 2.5D- und 3D -Chiplet -Modellintegration

- 1.8 Aufbau eines Ökosystems für erfolgreiche 2.5D- und 3D -Chiplet -Modellintegration

- 1.9 Das durchgesickerte Bild zeigt ein ehrgeiziges Design von Chiplet für die GPU Amd Radeon

- 1.10 Das durchgesickerte Bild zeigt ein ehrgeiziges Design von Chiplet für die GPU Amd Radeon

Einige Jahre später erschienen die ersten Prozessoren mit insbesondere mit dem Intel 4004, relativ einfach, heute relativ einfach. Dann wurden die Prozessoren komplexer.

Das Aufkommen von Chiplets

Nach einer Diskussion in JZDS und über die Zwietracht sagte ich mir, dass das Schreiben eines Artikels über die Chiplets für die größte Zahl von Vorteil sein würde. Und würde einen schriftlichen Track im Widerspruch zu dem halten, was mit den JZDs passieren kann

Anstatt ein sehr langes Ticket zu schreiben, bevorzuge ich das Format des Artikels, um ein wenig mehr in die Details einzugehen. Ich hoffe, Ihnen beibringen zu können, was die Chiplets sind, warum diese Technologie geschaffen wurde und warum sie sich in den kommenden Jahren entwickeln wird.

- Präambel

- Chiplet, Quésaco ?

- Wirtschaftliche Aspekte von Chiplets

- Zwei Beispiele: AMD und Intel (Altera)

Präambel

In diesem Artikel geht es um Computer-, Elektronik- und Architekturkonzepte von Computern, die für bestimmte Leser genug vorangetrieben werden können. Ich biete Ihnen eine kleine Popularisierung in dieser Präambel an, um ein bisschen besser zu verstehen, worüber wir sprechen.

Für Puristen werden Verknüpfungen vorgenommen. Diese Popularisierung kann möglicherweise freiwillig ungenaue Informationen enthalten, um das Verständnis zu erleichtern.

Chiplet, Quésaco ?

Beginnen wir mit dem schwierigsten und definieren Sie, was ein Chiplet ist !

In der Tat erschien der Begriff Chiplet in den 1970er Jahren, aber seine Verwendung hat sich hauptsächlich in den letzten Jahren für diejenigen angenommen, die an komplexen Prozessoren oder elektronischen Chips wie FPGA interessiert sind (Chips, deren interne logische Türen neu programmiert werden können). Für die anderen, am Ende des Raumes, haben Sie vielleicht noch nie von diesem Begriff gehört, wir werden ihn beheben !

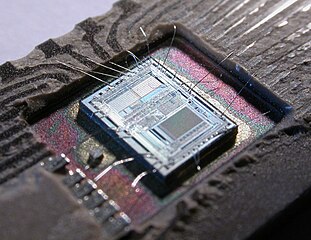

Kehren wir auf die Grundlage eines elektronischen Chips zurück: ein Stück gravierter Silizium (die berühmten Transistoren), das in einem Fall eingekapselt ist. Mit den Kreuzungskomponenten verbinden winzige Gold- oder Silberfäden die Beine der Komponente mit dem Stück Silizium. Zu Beginn bestehen die Chips aus Transistoren mit ziemlich groben Auflösungen (im Vergleich zu heute) und die Funktionen waren ziemlich einfach: logische Türen, operative Verstärker usw. Es war jedoch bereits ein enormer Fortschritt in Bezug auf die Miniaturisierung !

Zu dieser Zeit hatten die Komponenten Kreuzbeine und es ist notwendig, den Siliziumchip mit diesen Beinen zu verbinden. Es besteht aus dünnen Silber- oder Goldsöhnen, die zwischen dem Chip und den Beinen im Gehäuse geschweißt werden.

Einige Jahre später erschienen die ersten Prozessoren mit insbesondere mit dem Intel 4004, relativ einfach, heute relativ einfach. Dann wurden die Prozessoren komplexer.

Ab den 1970er Jahren entwickelte IBM MCM -Komponenten (Multi-Chodu) einschließlich mehrerer Siliziumchips in einem einzigen Fall. Diese Technologie wird sich jedoch hauptsächlich Ende der 90er Jahre entwickeln. Wir können den 1995 veröffentlichten Pentium Pro von Intel beachten. Dieser Prozessor enthielt zwei Siliziumchips: eine für den Prozessor streng genommen und eine für einen L2 -Cache -Speicher (ein Pufferspeicher zwischen dem Prozessor und dem RAM, viel schneller, aber viel teurer, weil mit dem Prozessor eingraviert ist).

Wie wir auf dem Foto sehen können, haben die beiden Chips ungefähr die gleiche Größe und Intel boten mehrere Größen Cache L2. Der Vorteil der Trennung des Cache -Speicherprozessor.

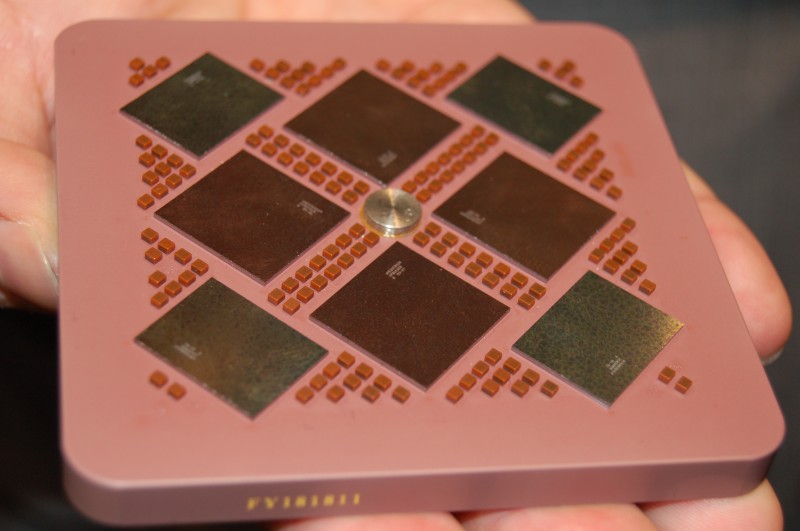

Diese Art von Komponente bleibt relativ unterentwickelt, auch wenn IBM weiterhin MCM -Komponenten entwickelt hat. Beachten Sie die im Jahr 2004 veröffentlichte Power5 von IBM, bei der vier Prozessoren mit einem Cache L3 -Speicherchip genau stehen. Die Vernetzung von Flöhen erfolgt im Inneren des Gehäuses.

Heute hat sich die Technologie weiterentwickelt und die MCM -Chips sind in Konsumgütern mit AMD -Prozessoren vorhanden. Hier sehen wir einen EPYC 7702 -Prozessor (veröffentlicht im August 2019), der aus 9 miteinander verbundenen Siliziumchips besteht: 8 Chips mit Kernen und Cache -Speicher und einen zentralen Chip, der die anderen 8 verbindet und die den DDR sowie den Signale D ‘Eingang/ Eingang verwaltet/ verwaltet Beenden (SATA, PCI Express, USB usw.)).

Aber sag mir Jamy, was ist ein Chiplet ?

Ah ja, ich habe ein wenig abgeleitet

Tatsächlich ist ein Chiplet einer der Siliziumchips, die in einem MCM vorhanden sind. Ein Chiplet wird so hergestellt, dass sie mit anderen Chiplets verbunden sind. Ja, es ist relativ einfach, aber Sie mussten einige schöne Fotos zeigen, um sie zu verstehen

Dennoch ist die Idee nicht unbedingt, mehrere verschiedene Chips miteinander zu verknüpfen, um die Bedeutung der Chiplets etwas genauer zu sein. Es gibt auch einen Begriff des generischen Chips, der wiederverwendet und nicht einer bestimmten Prozessorreferenz gewidmet werden kann.

Wirtschaftliche Aspekte von Chiplets

Lassen Sie uns nach dieser Einführung nun verstehen, warum sich die Chiplets in Zukunft entwickeln werden. Dazu ist es notwendig, zur Herstellung elektronischer Flöhe zurückzukehren.

Setzen Sie sich bequem in einem Sessel, denn die Reise vom Sandstrand wird lang sein

Nein, warte !

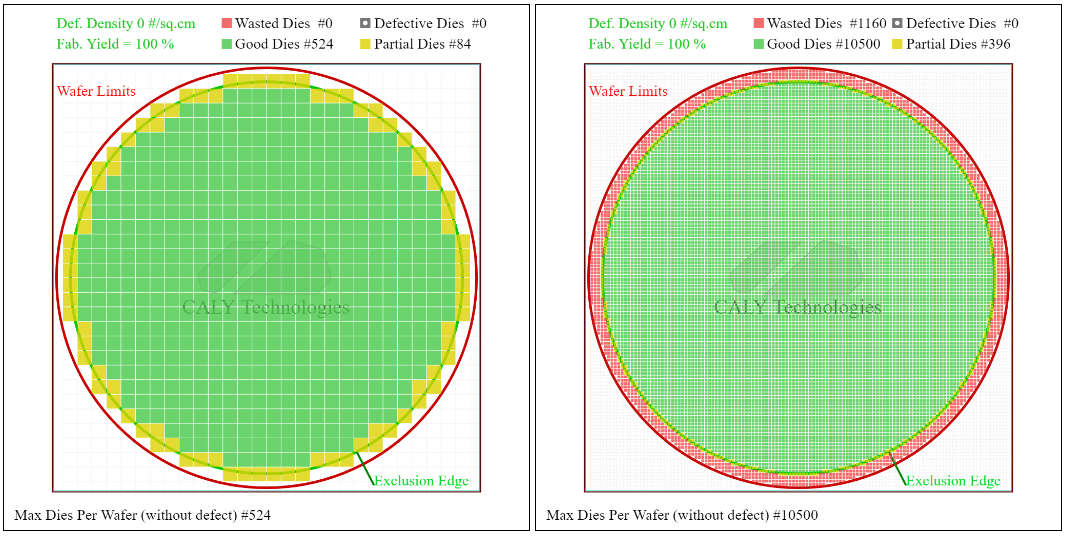

Wir werden einen ganzen Teil der Herstellung von Silizium verbringen. Was uns interessiert, ist die Verteilung von Flöhen (sterben) auf dem Siliziumkuchen (Wafer) und insbesondere die Evolution des Ertrags mit der Zunahme der Gravurfiniere.

Aber vor diesem Aspekt der Ertrag müssen wir über die maximale physische Größe eines Würfels sprechen. In der Tat wird bei einem Siliziumpfannkuchen das gleiche Design eines Chips mehrmals wiederholt (Zehn oder sogar hundertmal). Der Eindruck dieses Designs erfolgt optisch über ultraviolettes Licht. Es gibt jedoch eine ganze Reihe von Linsen und optischen Mechanismen, die verhindert.

Je mehr wir die Flöhe erschweren, desto mehr wollen wir Transistoren einsetzen, sodass wir entweder die Größe des Chips erhöhen oder die Delikatesse der Gravur erhöhen müssen, um mehr Transistoren in die gleiche Oberfläche zu stecken. Aber es sind auch andere Einschränkungen und Grenzen zu spüren.

Aus diesem Grund ist das Prinzip des Chiplets interessant, um diese Grenzen zu umgehen: Verwenden Sie mehrere kleine Silicum -Chips, die miteinander verbunden sind, um einen komplexeren Chip zu machen, aber unmöglich auf monolithische Weise zu gravieren.

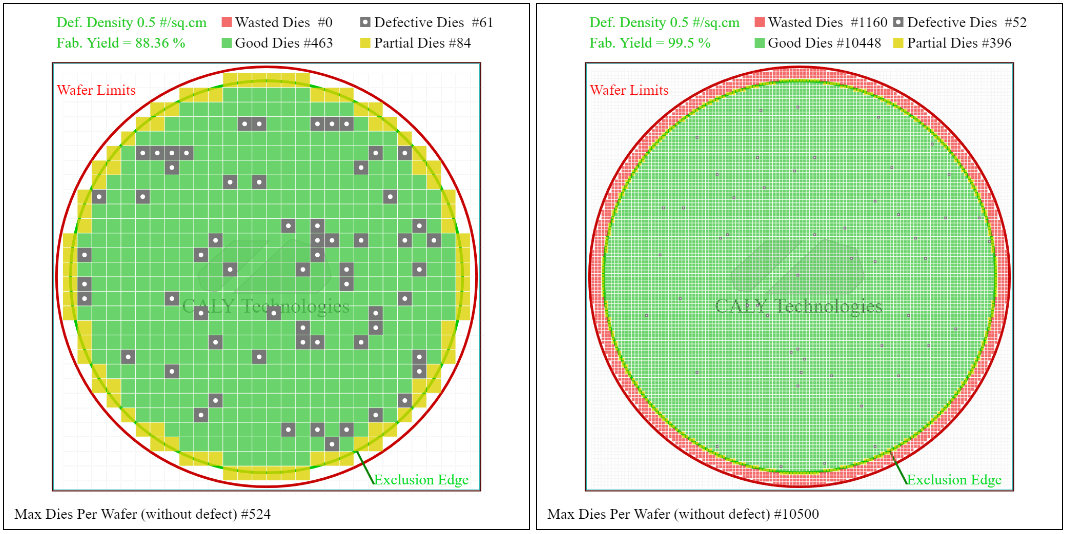

Jetzt zurück zum Rendite (Ertrag auf Englisch). Erstens sind die Wafer rund in Form und wir möchten sie mit rechteckigen Chips eingravieren. Das gesamte Silizium wird nicht verwendet. Aber je kleiner die Stirme an den Rändern und desto mehr können wir ganze Stanze haben. Es ist das gleiche Prinzip wie das Aliasing in einem Videospiel: Je mehr die Pixel, die zur Bildung einer runden Form verwendet werden.

Wenn wir im obigen Beispiel die Teilstimmungen an der Gesamtzahl der Stanze (gut und Voreingenommenheit) melden, erhalten wir ein Verhältnis von 13.8 % im Fall von 5 × 5 mm und 3.6 % im Fall von 1 × 1 mm stirbt. Je kleiner der Würfel ist, desto gültigere Stanze können an den Rändern haben, was den Ertrag erhöht.

Sie können auch ein großes Stempelmisch in der Mitte des Wafers herstellen und kleinere Stanze an den Rändern verwenden, um die Ausbeute aufgrund von Aliasing zu optimieren.

Sagen Sie Jamy, warum verwenden wir runde Wafer, um rechteckige Flöhe zu machen ?

Nun, es liegt an der Methode zur Herstellung von Silizium als Czochralski -Prozess, der Silizium in Form von Zylinder verleih Wafer.

Zweitens wird die Ausbeute durch die Defekte beeinflusst, die auf dem Wafer erscheinen können. Sie können sich Staubkörner vorstellen, die auf den Wafer fallen.

Ich habe das vorherige Beispiel wieder aufgenommen, indem ich eine Fehlerdichte von 0 hinzufügte.5 pro cm². Vergleichen Sie nun die Ertragsfertigung Dies entspricht dem Verhältnis zwischen der Anzahl der funktionellen Stanze und der Gesamtzahl der produzierten Produkte. Im Falle einer 5 × 5 mm -Sterbe beträgt die Ausbeute 88.4 %, während mit 1 × 1 mm Sterben die Ausbeute 99 beträgt.5 %.

Es ist daher doppelt interessant, kleine Stanze zu haben, um die Produktion von elektronischen Flöhen zu optimieren. Das Schneiden eines komplexen Chips in mehrere kleinere Chips erfordert jedoch die Kommunikation dieser verschiedenen Chips zwischen ihnen.

Darüber hinaus kann die Verwendung von Chiplets es ermöglichen, Stempel aus verschiedenen Gravierstörungen entsprechend den Funktionen zu verwenden, die es ermöglichen, die Kosten des letzten Chips mit der Leistung zu modulieren.

Ein weiterer wirtschaftlicher Aspekt ist die Komplexität der Entwicklung neuer Merkmale. Dies hat in der Regel spezielle Unternehmen (oder zumindest zu Beginn Start-ups), die geistige Immobilienblöcke (Funktionen) anbieten, die verwendet werden können. Beispielsweise kann sich ein Prozessorhersteller auf die Entwicklung des Prozessors selbst konzentrieren, während er Stanze für Funktionen wie PCI Express-, USB- oder DDR -Controller kauft.

Um die Interoperabilität von Chiplets von verschiedenen Herstellern zu erleichtern, haben Hauptakteure wie Intel, AMD, ARM, Qualcomm, Samsung oder TSMC einen Kommunikationsstandard zwischen Chipplets, UCIE (geschaffenUniversal Chiplet Interconnect Express)).

Zwei Beispiele: AMD und Intel (Altera)

AMD EPYC

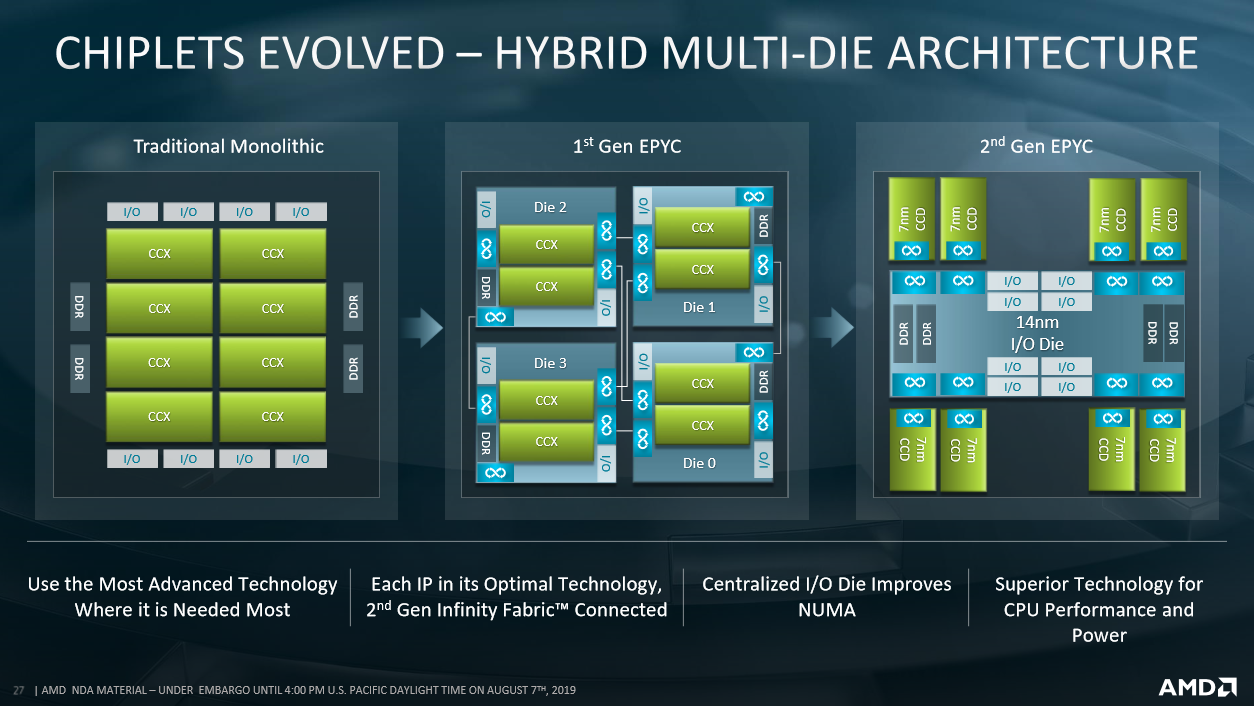

Heute verwenden immer mehr Prozessoren diese Chiplets -Technik. AMD verwendet Chiplets seit der ersten Generation von EPYC -Prozessoren, bei denen die verschiedenen Herzen durch die miteinander verbunden sindInfinity Stoff.

Die erste Generation von EPYC -Prozessoren sah eine Reihe von Würfel, die mit vollständigen Prozessoren gleichgesetzt werden konntenInfinity Stoff Um den endgültigen Prozessor zu bilden. Die Chiplets waren daher eine Art kleiner autonomer Prozessor: Jeder Der verwaltete seine Einträge/Ausgaben und hatte seinen DDR -Controller.

Diese Sterben oder vielmehr haben Chiplets zwei Kernkomplex (CCX, ein Satz von vier Kernen mit Cache -Speicher) sowie ein DDR -Controller, verwaltet Eingänge/Ausgänge (z. B. PCI Express) und verfügt über Kommunikationsmodule für dieInfinity Stoff.

Kleine Subtilität, es gibt immer vier Chiplets in einem EPYC der ersten Generation. Um die Anzahl der Herzen zu variieren, deaktiviert AMD die Herzen in CCX. Zum Beispiel, um 24 Kerne zu haben, haben CCX nur 3 aktive Kerne

Diese erste Generation verwendete daher das Prinzip der Chiplets als eine Art Kopie/Kleber von Stanze, anstatt einen großen monolithischen Würfel zu entwickeln.

Für die zweite Generation drückt AMD das Konzept etwas weiter voran. In der Tat sind die CCXs jetzt unabhängig und paaren sich paarweise innerhalb von a Kernberechnung sterben (CCD) verbunden durch Infinity Stoff zu einem sterbe, der den DDR und die Einträge/Ausgänge verwaltet E/O sterben (IOD).

AMD nutzt diese erhöhte Trennung von Funktionen vollständig aus. In der Tat ist der CCD in 7 nm eingraviert, während der IOD in 14 nm eingraviert ist.

Unterhalb einer AMD -Präsentation zusammenfasst die Passage in Chiplets der EPYC -Prozessoren.

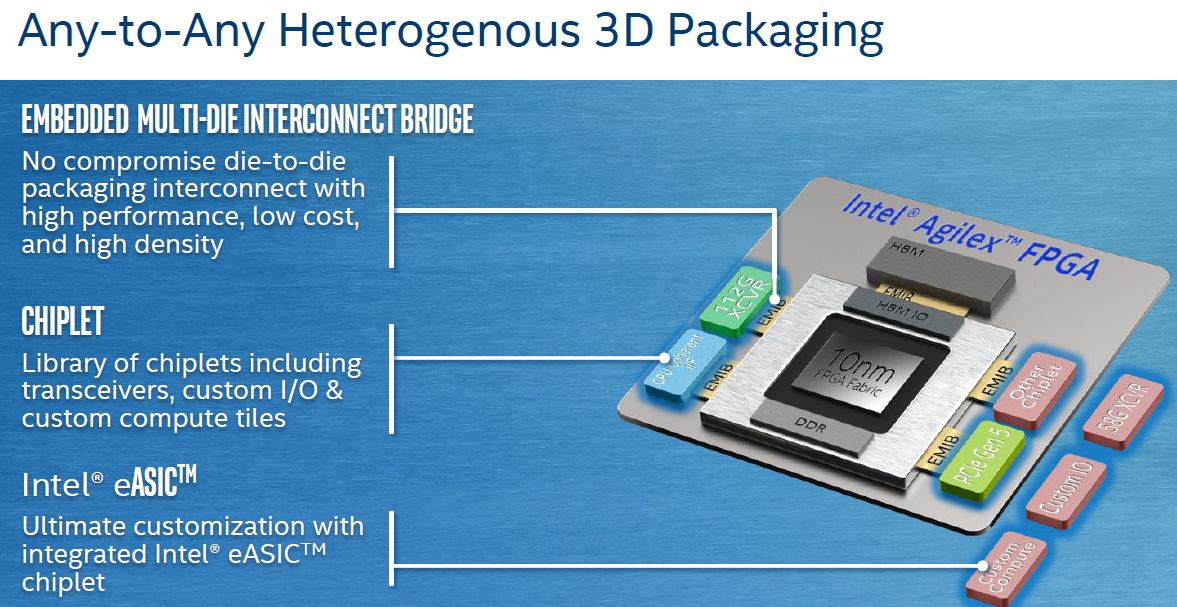

Intel FPGA (Altera)

Intel -Prozessoren sind immer monolithische Chips mit Ausnahme einiger Ausnahmen, wie wir zu Beginn dieses Artikels sehen konnten. Trotzdem verwendet der Intel FPGA -Sektor (Rekonfigurierbares FPGA) Chiplets für die neueste Generation Agilex.

Diese Chiplets betreffen hauptsächlich die Art der verwendeten Transzense (schnelle Links) und werden genannt Fliesen. Wenn Intel vordefinierte Bereiche von diesen Kacheln anbietet, muss es möglich sein, individuelle Chips für Ihre eigenen Bedürfnisse zu haben.

Die Fliesen werden durch die maximale Geschwindigkeit der Transceiver und der unterstützten Protokolle geteilt (Ethernet, PCI Express usw.): 16 g für p, 28g für H, 32 g für R, etc.

Intel rührt auch für die Zukunft die Möglichkeit, angepasste Chiplets mit zusätzlichen Funktionen zu verbinden, die zusätzliche Funktionen bieten würden. Derzeit haben Unternehmen ein ADC/DAC -Chiplet (JARIETT Technologies) sowie eine weitere optische Verbindung (Ayar Labs) veröffentlicht.

Schließlich dürfen wir auch nicht glauben, dass die Chips monolithisch sind tot. Sie haben immer Vorteile, insbesondere in Bezug auf interne Kommunikation und Latenz, die für bestimmte Anwendungen, die große Chips erfordern, von entscheidender Bedeutung sein können.

Dies ist der Fall von Broadcom und seinem Switch 400G Chips, deren Auswahl vom Designer in diesem Video erklärt wird: https: // www.Youtube.Com/Uhr?V = b-cogmbaug4

Ich hoffe. Ich habe versucht, ein komplexes Thema bekannt zu machen. Ich hoffe auch, dass ich Sie nach dem ersten Absatz behalten konnte

Zögern Sie nicht, einen Kommentar zu hinterlassen, wenn bestimmte Punkte für Sie kryptisch bleiben. Ich werde versuchen, Details anzugeben.

6 Kommentare

Diese Antwort war nützlich

Ausgezeichneter Artikel, danke @ zeql !

“Wirf mich in die Wölfe und ich werde das Rudel zurückgeben.” – Seneca

Diese Antwort war nützlich

Ich habe mich gefragt, wie sehr das Aufkommen der Chiplets eine bestimmte Entwicklung in der Hardware in Betracht ziehen konnte (auch Verbraucher Das Serverqualität) in Zukunft oder sogar eine Paradigmenverschiebung auf der Art und Weise, wie wir insgesamt starke und optimale Maschinen entwerfen.

Bestimmte gut integrierte Systeme (insbesondere bei Apple) basieren nicht nur auf einer sehr effizienten „klassischen“ CPU, sondern auch auf mehreren spezialisierten Hilfschips, die den Generalist CPUs entladen. In einem begrenzten System als Smartphone finden wir H265 -Transkodierungschips, Berechnungseinheiten für AI (Apple Neural Motor) und natürlich die klassische Grafikeinheit.

Ich nehme daher das Diagramm von AMD EPYC der 2. Generation auf und frage. Zum Beispiel könnte eine Einheit klassische CCDs, aber auch eine DSP, eine GPU, transco H265/AV1/VP9/…, einen Chip zum AES usw. liefern. und verbinden Sie alles über IOD/Infinity Manufacture. Jeder Hersteller von Maschinen/Servern könnte daher seine endgültige endgültige Einheit bestimmen, indem sie sich und ohne R & D/Faraminurous-Industrialisierungskosten komponiert haben.

Es erinnert mich an das Konzept der APU, aber ich weiß nicht, ob es einen Bericht gibt.

Diese Antwort war nützlich

Ich habe mich gefragt, wie sehr das Aufkommen der Chiplets eine bestimmte Entwicklung in der Hardware in Betracht ziehen konnte (auch Verbraucher Das Serverqualität) in Zukunft oder sogar eine Paradigmenverschiebung auf der Art und Weise, wie wir insgesamt starke und optimale Maschinen entwerfen.

Bestimmte gut integrierte Systeme (insbesondere bei Apple) basieren nicht nur auf einer sehr effizienten „klassischen“ CPU, sondern auch auf mehreren spezialisierten Hilfschips, die den Generalist CPUs entladen. In einem begrenzten System als Smartphone finden wir H265 -Transkodierungschips, Berechnungseinheiten für AI (Apple Neural Motor) und natürlich die klassische Grafikeinheit.

Ich nehme daher das Diagramm von AMD EPYC der 2. Generation auf und frage. Zum Beispiel könnte eine Einheit klassische CCDs, aber auch eine DSP, eine GPU, transco H265/AV1/VP9/…, einen Chip zum AES usw. liefern. und verbinden Sie alles über IOD/Infinity Manufacture. Jeder Hersteller von Maschinen/Servern könnte daher seine endgültige endgültige Einheit bestimmen, indem sie sich und ohne R & D/Faraminurous-Industrialisierungskosten komponiert haben.

Es erinnert mich an das Konzept der APU, aber ich weiß nicht, ob es einen Bericht gibt.

Sie sollten also wissen, dass ein Chip häufig mit IP (geistiges Eigentum) durchgeführt wird: eine Funktion, die auf der Ebene “Transistoren” ziemlich fertiggestellt ist, die jedoch in sein Design integriert werden muss.

Ein klassisches Beispiel ist ein DDR3 -Controller auf -board -Mikrocontroller. Der Hersteller des Mikrocontrollers beherrscht den DDR3 nicht unbedingt und verfügt nicht über die Fähigkeiten, die Zeit (weder den Wunsch), einen DDR3 -Controller zu erstellen. Er kauft daher eine IP von einem Controller und integriert ihn in sein Design.

Es muss Ihnen gelingen, den Unterschied zwischen der Möglichkeit eines IP und einem Chiplet zu erkennen. Für mich ist das Chiplet da und ein oder mehrere fortgeschrittene Funktionen mitbringen, die bereits die Tests des Gravurs bestanden haben, daher ein zusätzlicher Schritt im Design. Aber es bleibt das Problem, den vollen Boden mit allen Chiplets zu testen. Wir können also keine Hunderte von Variationen wie ein LEGO erstellen. Es dauert ein Minimum der wirtschaftlichen Realität.

Aber ja, für ein bestimmtes Volumen können wir à la carte Sockets erstellen.

Der große Vorteil liegt auf der Produktionsseite des Chip mit kleinerem Gravur verbessert werden.

Diese Antwort war nützlich

Außerdem dachte ich, dass die Chiplets in einem modularen Design verwendet werden könnten. Sie nehmen ein Design mit 4 Chips, die Flöhe mit Fehlern werden während der gesamten Produktion verteilt, und diejenigen mit 3 Chips, die an 4 arbeiten.

Dies vereinfacht das Design und die Industrialisierung in Bezug auf den konventionellen Betrieb.

Liebhaber freier Software und GNU/Linux Fedora Distribution. #Jesuisarius

Diese Antwort war nützlich

Vielen Dank für diesen interessanten Mega -Artikel. Ich würde dich zu viel Zeit lieben, um jeden Punkt zu detailliert, den du im Tutorial nicht erklärst, um Dinge wirklich zu verstehen, aber sowieso interessant .

Verwenden von Chiplet -Design -Kits, um den Weg für die heterogene 3D -IC -Integration zu ebnen

Ein Chiplet ist ein ASIC -Würfel, der speziell entworfen und für den Betrieb innerhalb eines Pakets in Verbindung mit anderen Chiplets optimiert wurde. Heterogene integrierte (HI) beinhaltet enge Mehrfachst Die oder Chiplets in System-in-Package (SIP) -Schipplets. Diese Geräte beinhalteten angesehene Vorteile, umfassten Leistung, Strom, Bereich, Kosten und TTM.

Das Chiplet Design Exchange (CDX) besteht aus EDA -Anbietern, Chiplet

Anbieter/Assembler und SIP -Integratoren und ist eine offene Arbeitsgruppe, die standardisierte Chiplet -Modelle und Workflows empfiehlt, um ein Chiplet -Ökosystem zu erleichtern. Dieses Webinar fasst die Chiplet Design -Kits (CDKs) zusammen, um 2 zu standardisieren 2.5d und 3.D ic Designs zum Erstellen eines offenen Ökosystems.

Aufbau eines Ökosystems für erfolgreiche 2.5D- und 3D -Chiplet -Modellintegration

Ähnlich wie bei einem SOC -Prozess benötigen Sie ein Ökosystem für Chipplets. Schlüssel zur allgemeinen Markteinführung und Bereitstellung von auf Chiplet -basierten Designs, die inklusive Entwürfe basieren, werden: Folge:

- Technologie: 2.5 d Interposition und 3D gestapelte Herstellungs- und Montageprozesse

- IP: Standardisierte Chiplet -Modelle

- Workflows: EDA Design Flows und PDK-, CDK-, DRM- und Montage -Regeln

- Geschäftsmodelle: Chiplet Marketplace

Der anfängliche Fokus des CDX liegt 2.5D interposierungsbasierte Chiplet-Modelle mit 3D, die folgen sollen. Erfahren Sie mehr über diese Bemühungen im Webinar.

Das Chiplet Design Exchange (CDX) besteht aus EDA -Anbietern, Chiplet -Anbietern/-Anterbietern und SIP -Integratoren und ist eine offene Arbeitsgruppe, die standardisierte Chiplet -Modelle und Workflows empfiehlt, um ein Chiplet -Ökosystem zu erleichtern. Dieses Webinar fasst die Chiplet Design -Kits (CDKs) zusammen, um 2 zu standardisieren 2.5d und 3.D ic Designs zum Erstellen eines offenen Ökosystems.

Aufbau eines Ökosystems für erfolgreiche 2.5D- und 3D -Chiplet -Modellintegration

Ähnlich wie bei einem SOC -Prozess benötigen Sie ein Ökosystem für Chipplets. Schlüssel zur allgemeinen Markteinführung und Bereitstellung von auf Chiplet -basierten Designs, die inklusive Entwürfe basieren, werden: Folge:

- Technologie: 2.5 d Interposition und 3D gestapelte Herstellungs- und Montageprozesse

- IP: Standardisierte Chiplet -Modelle

- Workflows: EDA Design Flows und PDK-, CDK-, DRM- und Montage -Regeln

- Geschäftsmodelle: Chiplet Marketplace

Der anfängliche Fokus des CDX liegt 2.5D interposierungsbasierte Chiplet-Modelle mit 3D, die folgen sollen. Erfahren Sie mehr über diese Bemühungen im Webinar.

Das durchgesickerte Bild zeigt ein ehrgeiziges Design von Chiplet für die GPU Amd Radeon

Das durchgesickerte Bild zeigt ein ehrgeiziges Design von Chiplet für die GPU Amd Radeon

- von

- In Nachrichten

- am 16. August 2023

Ein durchgesickertes Bild ist aufgetaucht und enthüllt ein GPU -Design mit Radeon -Chiplets, angeblich aus einem abgebrochenen Projekt des NAVI 4C -Chips 4C. Das Design vorhanden zwischen 13 und 20 verschiedenen Chiplets einer einzelnen GPU, die den ehrgeizigen AMD -Ansatz aussagen. Dieses komplexere Chiplet -Design unterscheidet sich vom Navi 31 -Silizium, das derzeit im Radeon RX 7900 XTX verwendet wird. Während die vorherige Iteration der GPU als erste Generation angesehen wurde, verwendete sie kein echtes Chiplet -Design wie die jüngsten Ryzen -Prozessoren von AMD. Die Konzeption von NAVI 4C, die offenbart wurde. Das durchgesickerte Bild zeigt 13 Chiplets, wobei die Möglichkeit zusätzlicher Speichercontroller -Chips auf dem Bild nicht angezeigt werden.

Um die Echtheit des Bildes zu bestätigen, wird ein relevantes Patent von 2021 hervorgehoben. Die Patentmuster ähneln stark dem im durchgesickerten Bild gezeigten Design, was sogar auf die Möglichkeit von mehr Chiplets auf der anderen Seite der Querbecher hinweist.

Leider wurde das im durchgesickerte Bild vorgestellte Design der GPU abgebrochen. Dies stimmt mit den jüngsten Beziehungen überein, die darauf hindeuten. Es wird jedoch spekuliert, dass AMD seine Bemühungen auf die Entwicklung einer GPU, die aus mehreren Berechnungschiplets für das hohe Segment seines zukünftigen Grafikkartens besteht, umgerichtet wird, möglicherweise mit rDNA 5.

Obwohl die Realisierung mehrerer Berechnungschiplets für Spielgrafiken komplexer ist als für herkömmliche CPU -Berechnungen, wird die Entscheidung von AMD, die Entwurfshindernisse jetzt zu überwinden, und die Arbeit an einer besseren Lösung für rDNA 5 als positiver Schritt wahrgenommen. Für AMD wäre es vorteilhaft gewesen, einen Rettungsplan wie einen neuen Knoten für eine verbesserte Version von NAVI 31 zu haben.